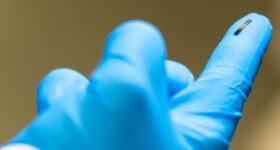

A TSMC, maior fabricante de semicondutores do mundo, já confirmou que deve iniciar a produção de wafers de 2 nanômetros até o fim de 2025.

Porém, a empresa não quer parar por aí e já está se preparando para um processo ainda mais avançado: o de 1,4 nanômetro, também chamado de A14.

De acordo com um novo relatório, a companhia pretende começar as etapas iniciais de construção de sua fábrica voltada a essa tecnologia em Taiwan, mas sem depender das caríssimas máquinas High-NA EUV da ASML, conhecidas por serem as mais sofisticadas do mercado.

Em vez de investir nessas novas máquinas, a TSMC planeja usar técnicas complexas de multi-patterning — um método que combina várias exposições para atingir o nível de precisão necessário na fabricação dos chips.

Segundo o jornal Commercial Times, a empresa deve iniciar as obras da nova planta em Taichung até o fim deste ano. A produção em massa, porém, só deve começar na segunda metade de 2028.

Esse cronograma já havia sido mencionado antes e inclui a promessa de que o processo A14 pode reduzir o consumo de energia dos chips em até 30%.

A pesquisa e o desenvolvimento dessa nova tecnologia serão conduzidos na unidade da TSMC em Hsinchu, enquanto o recrutamento de profissionais já começou em Taichung. As licenças de construção para três prédios foram aprovadas em agosto.

Para tirar o projeto do papel, o investimento inicial da empresa deve chegar a cerca de NT$ 1,5 trilhão, o equivalente a aproximadamente US$ 49 bilhões. Grande parte desse valor deve ser destinada à compra de 30 máquinas de litografia EUV em 2027.

De acordo com Dan Nystedt, em uma publicação no X (antigo Twitter), a TSMC não pretende adquirir os equipamentos High-NA EUV da ASML — cada um avaliado em cerca de US$ 400 milhões.

O custo altíssimo é um dos principais motivos dessa decisão. Além disso, a empresa já disse que seus equipamentos atuais são capazes de produzir wafers de 1,4nm em larga escala. Assim, a aposta no multi-patterning parece uma estratégia mais equilibrada entre custo e viabilidade técnica.

Esse método alternativo também tem suas desvantagens. O processo é mais demorado, caro e pode gerar um rendimento inicial baixo — ou seja, menos chips aproveitáveis por lote. Por isso, a TSMC deve adotar uma abordagem de "tentativa e erro" para aperfeiçoar gradualmente a produção.

Ainda assim, a empresa leva vantagem sobre concorrentes como a SMIC, que também usa o multi-patterning para fabricar chips de 5nm, mas não possui a mesma infraestrutura de litografia EUV que a TSMC já domina.

Como a produção em massa dos chips de 1,4nm ainda está a alguns anos de distância, a TSMC tem tempo de sobra para refinar o processo e manter sua liderança na corrida global da miniaturização dos semicondutores.