O Instituto Coreano de Engenheiros de Semicondutores divulgou previsões para a evolução do silício nos próximos 15 anos por meio do documento "Semiconductor Technology Roadmap 2026".

O material aponta que, até 2040, os circuitos semicondutores podem chegar ao processo de 0,2 nanômetro, entrando na chamada era do angstrom.

Hoje, o menor processo anunciado publicamente é o de 2 nanômetros com tecnologia Gate-All-Around, usado no chipset Exynos 2600 da Samsung.

Para que a indústria alcance patamares abaixo de 1 nanômetro, ainda será necessário avançar bastante em pesquisa, processos industriais e materiais, já que existem muitos obstáculos técnicos ao longo do caminho.

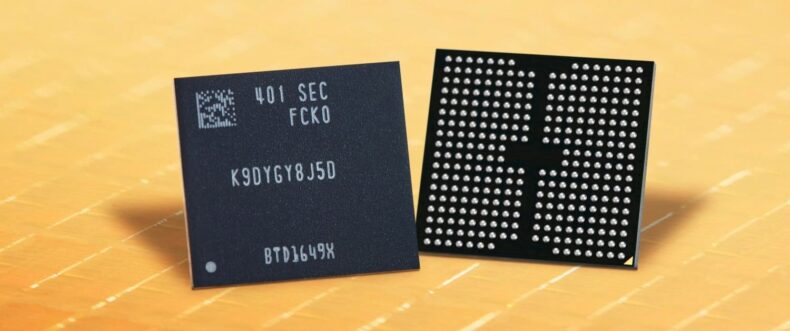

O estudo também traz projeções para outras áreas do setor. A expectativa é que as memórias NAND flash passem das atuais 321 camadas para até 2.000 camadas no futuro.

Já os semicondutores voltados para inteligência artificial tendem a alcançar desempenho de dezenas de trilhões de operações por segundo, acompanhando a crescente demanda por processamento em tarefas de aprendizado e inferência.

Segundo informações publicadas pelo ETNews, o objetivo do roadmap é fortalecer a tecnologia de semicondutores no longo prazo, aumentar a competitividade da indústria, estimular pesquisas acadêmicas e apoiar estratégias de formação de profissionais.

O plano apresentado pelo instituto abrange nove áreas centrais, como dispositivos e processos semicondutores, chips para inteligência artificial, semicondutores para conexões ópticas, sensores com conexão sem fio, tecnologias de conexão por fio, soluções de integração, encapsulamento e computação quântica.

- Leia tambem: Samsung e SK hynix usam estratégias diferentes para desenvolver nova geração de memória DRAM voltada para IA

Atualmente, a menor litografia em produção pertence à Samsung, com o processo de 2 nanômetros baseado em GAA. A empresa já trabalha em versões mais avançadas dessa tecnologia.

O desenho básico da segunda geração do nó de 2 nanômetros foi concluído, e a terceira geração, conhecida como SF2P+, deve entrar em operação dentro de cerca de dois anos.

Para 2040, a estimativa é que o processo de 0,2 nanômetro utilize uma nova estrutura de transistor chamada CFET, sigla para Complementary Field Effect Transistor, combinada com um design monolítico em 3D.

A Samsung, considerada a principal referência da Coreia do Sul em fabricação de semicondutores de próxima geração, também teria criado uma equipe dedicada ao desenvolvimento de chips de 1 nanômetro.

A meta de produção em larga escala estaria prevista para 2029. Essas mudanças não ficariam restritas aos sistemas em chip usados em celulares.

As memórias DRAM também devem passar por redução no tamanho dos circuitos, saindo de 11 nanômetros para 6 nanômetros.

No caso da memória de alta largura de banda, a evolução apontada vai de 12 camadas com 2 terabytes por segundo para até 30 camadas e largura de banda de 128 terabytes por segundo.

No segmento de NAND, onde a SK hynix já alcançou a tecnologia QLC com 321 camadas, o avanço esperado permitiria chegar a 2.000 camadas no futuro.

Por fim, o relatório menciona os processadores de inteligência artificial. Hoje, esses chips conseguem atingir cerca de 10 trilhões de operações por segundo.

Dentro de aproximadamente 15 anos, a projeção indica componentes capazes de gerar 1.000 trilhões de operações por segundo em tarefas de aprendizado e 100 trilhões de operações por segundo em processos de inferência.