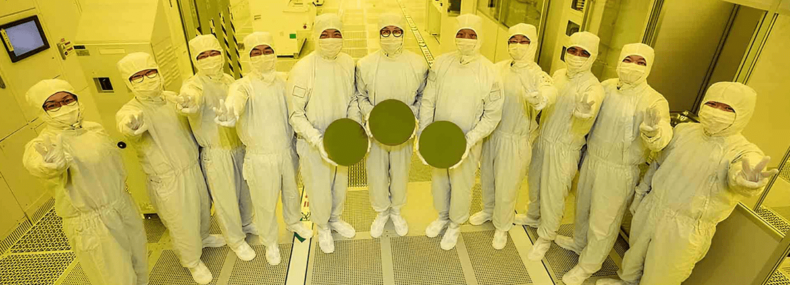

A Samsung está apostando na sua tecnologia de 2nm de última geração para se destacar no mercado de semicondutores, que deverá entrar em produção em massa em 2025.

A empresa coreana está desenvolvendo uma nova tecnologia chamada Backside Power Supply (BSPDN), que promete oferecer vários benefícios em termos de desempenho, eficiência e densidade dos chips.

Essa tecnologia já foi testada com sucesso em dois núcleos ARM, segundo um relatório da Chosun. A tecnologia BSPDN consiste em colocar as linhas de energia na parte de trás do wafer, separando-as do circuito que fica na parte da frente.

Isso permite reduzir a interferência entre os sinais e a alimentação, além de otimizar o espaço e a eficiência dos transistores.

Atualmente, as linhas de energia ficam na parte de cima do wafer, junto com o circuito, o que dificulta o projeto e a fabricação de chips com nós avançados, como o de 2nm.

Com essa tecnologia, a Samsung conseguiu reduzir a área do chip dos dois núcleos ARM em 10% e 19%, respectivamente, ao mesmo tempo em que aumentou o desempenho e a eficiência energética em até 9%.

Esses resultados superaram as expectativas da empresa, que espera ter uma vantagem competitiva sobre a sua rival TSMC, que também está trabalhando no processo de 2nm, mas sem a tecnologia BSPDN.

A Samsung já recebeu o primeiro pedido de chips de 2nm de uma startup japonesa, mas não revelou se usou a tecnologia BSPDN nesse lote.

A empresa planeja aplicar essa tecnologia em diversos segmentos, como dispositivos móveis, computação de alto desempenho e automotivo.

A Samsung espera que a sua tecnologia de 2nm seja uma revolução no mercado de semicondutores, assim como foram as suas inovações anteriores, como o processo GAA de 3nm e o MBCFET de 5nm.