Pense na DRAM, mas organizada em uma estrutura parecida com NAND. Esse é o conceito básico da 3D X-DRAM, uma proposta voltada ao mercado de memória, com foco em maior densidade para uso em IA.

3D X-DRAM se aproxima da realidade como alternativa ao HBM com maior densidade para IA

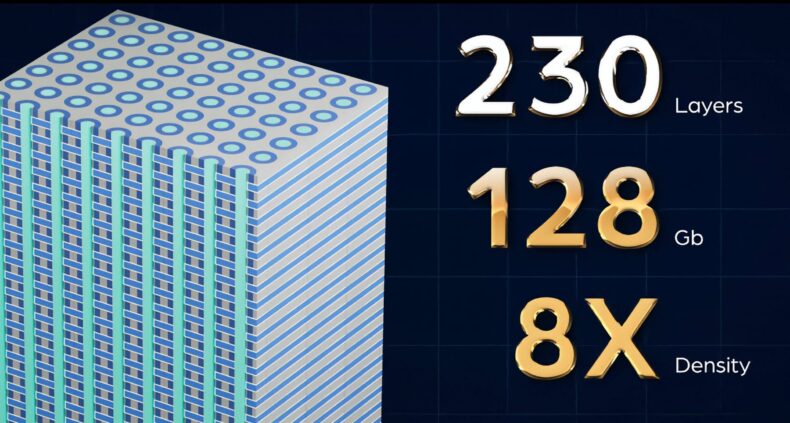

Em 2023, a empresa americana NEO Semiconductor anunciou um novo projeto chamado 3D X-DRAM. A ideia é contornar o limite de capacidade da DRAM usando uma arquitetura em 3D semelhante à NAND.

A empresa também apresentou dois tipos de células 3D X-DRAM, que devem ser usados em soluções baseadas nessa tecnologia.

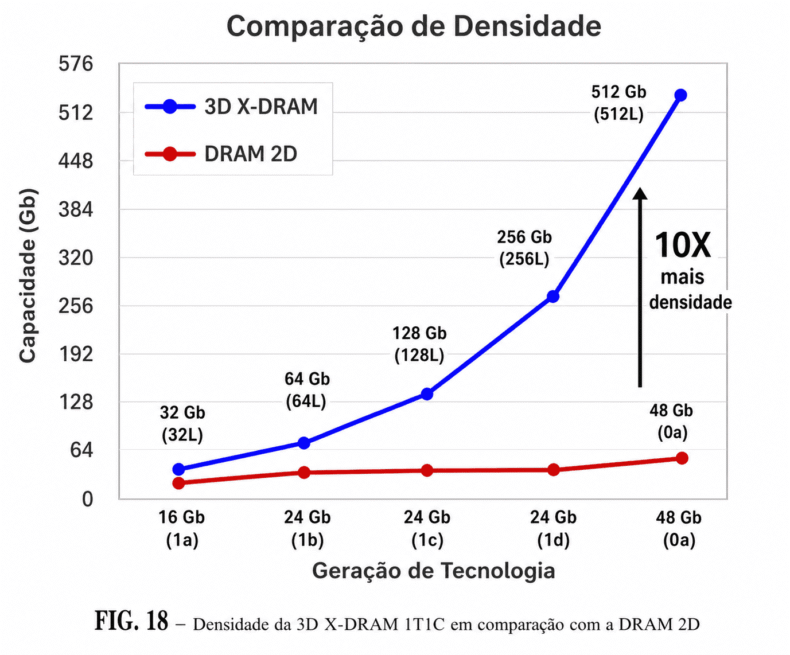

Essas células incluem os modelos 1T1C e 3T0C, com capacidade de até 512 Gb, cerca de 10 vezes mais densidade em comparação com a DRAM tradicional. A proposta também considera custo e produção em larga escala.

Cada variante foi pensada para usos diferentes. O modelo 1T1C segue os padrões de DRAM e HBM e foca em alta densidade. Já o 3T0C é voltado para cargas de trabalho de IA.

- 1T1C (um transistor, um capacitor) – solução principal para DRAM de alta densidade, compatível com padrões atuais de DRAM e HBM.

- 3T0C (três transistores, zero capacitor) – voltado para operações baseadas em leitura de corrente, indicado para IA e computação em memória.

- 1T0C (um transistor, zero capacitor) – estrutura com corpo flutuante, adequada para DRAM de alta densidade, computação em memória, memória híbrida e arquiteturas lógicas.

Entre os principais pontos do anúncio estão:

- Retenção e eficiência – com tecnologia de canal IGZO, simulações indicam retenção de até 450 segundos, o que reduz a necessidade de atualização constante dos dados.

- Validação por simulação – testes com Technology Computer-Aided Design indicam leitura e gravação em cerca de 10 nanossegundos e retenção acima de 450 segundos.

- Produção compatível – usa um processo adaptado de NAND 3D, com poucas mudanças, o que facilita integração em linhas já existentes.

- Alta largura de banda – arquitetura com técnicas de conexão híbrida que aumentam a taxa de transferência e reduzem consumo de energia.

- Desempenho em cargas avançadas – voltada para IA, computação de borda e processamento em memória, com acesso rápido e menor gasto de energia.

![]()

Uma vantagem da DRAM em relação à High-Bandwidth Memory é a facilidade de produção. O HBM é comum em IA e computação de alto desempenho, mas tem custo alto e exige muitos testes antes do uso em servidores.

Já a DRAM é mais simples de fabricar e validar. A 3D X-DRAM usa uma estrutura parecida com um único chip, diferente do HBM, que empilha vários chips de memória.

Agora, a NEO Semiconductor mostrou um protótipo funcional da 3D X-DRAM e conseguiu investimentos para seguir com o projeto.

Nos testes, a empresa indicou que a tecnologia pode ser produzida usando a infraestrutura atual de NAND 3D, com várias camadas de DRAM no mesmo chip, em vez de empilhamento como no HBM.

Os primeiros resultados dos chips de teste foram:

- Latência de leitura/gravação: menor que 10 ns

- Retenção de dados: acima de 1 segundo a 85 °C (cerca de 15 vezes mais que o padrão de 64 ms da JEDEC)

- Interferência de bit-line: acima de 1 segundo a 85 °C

- Interferência de word-line: acima de 1 segundo a 85 °C

- Durabilidade: mais de 10¹⁴ ciclos

Com a demanda crescente por memória em IA e computação de alto desempenho, soluções mais avançadas de DRAM passam a ser necessárias. A Intel também trabalha em uma proposta semelhante chamada ZAM (Z-Angle Memory).

Por enquanto, nenhuma dessas tecnologias está em produção, mas o avanço e os investimentos indicam que podem chegar ao mercado de servidores ainda nesta década.