Os próximos processadores Intel Diamond Rapids da linha Xeon devem adotar um novo desenho interno baseado em dois blocos separados, identificados pelos codinomes CBB e IMH.

As informações surgiram a partir de atualizações encontradas em patches do kernel, que indicam como será a base técnica dessa nova geração voltada a servidores e data centers.

O tile CBB, sigla para Core Building Block, será responsável pelo processamento. A principal mudança em relação ao Granite Rapids está na organização do controlador de memória.

Nos chips anteriores, esse componente ficava no mesmo bloco de computação. No Diamond Rapids, ele passa a ficar separado. O controlador de memória integrado, conhecido como IMC, fará parte do tile IMH, chamado de Integrated I/O and Memory Hub.

Esse bloco reúne funções de entrada e saída junto com o controle de memória e funciona de forma independente do CBB. As informações apontam que o Diamond Rapids pode ter até dois tiles IMH no mesmo processador.

Há indícios de que esses blocos fiquem posicionados no tile base, seguindo uma lógica parecida com a usada no Clearwater Forest.

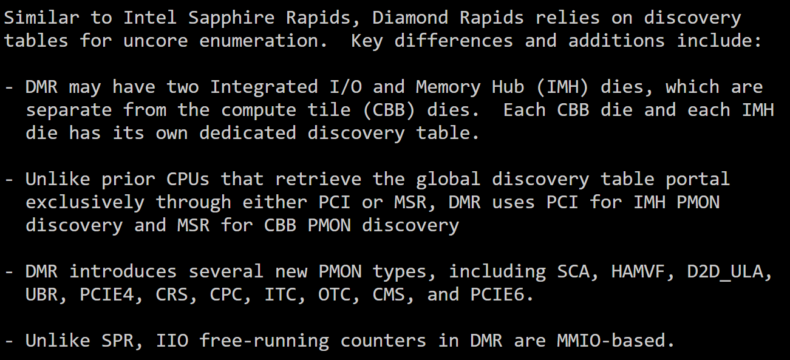

Assim como aconteceu no Sapphire Rapids, o Diamond Rapids usa tabelas de descoberta para identificar os componentes internos fora do núcleo principal. A diferença está na forma como isso acontece.

Cada tile CBB e cada tile IMH tem sua própria tabela dedicada. O acesso a essas informações também muda: o sistema usa PCI para a parte de monitoramento do IMH e registros MSR para o monitoramento do CBB.

Além disso, a nova geração passa a trabalhar com vários tipos novos de PMON e troca os contadores livres do bloco de I/O, que agora usam MMIO em vez do método anterior. Outro ponto citado nos registros é o suporte ao PCI Express 6.0.

Insightful Linux kernel patch:#Intel #DiamondRapids CPU chip = Core Building Block (CBB) and unlike #GNR they do not have an IMC.#DMR can have a chip with two "Integrated I/O and one memory hub (IMH)".

DMR goes even further than #CWF the IMC is on the Base Tile.

1/2 pic.twitter.com/0jHPUD3hJX— InstLatX64 (@InstLatX64) January 2, 2026

Essa tecnologia já havia sido anunciada para chegar ao mercado em 2026 e deve aparecer em plataformas de servidores de próxima geração, como o próprio Diamond Rapids e também o Venice.

De acordo com dados divulgados anteriormente, os processadores Intel Diamond Rapids Xeon devem chegar com até 192 núcleos, com rumores indicando versões que podem alcançar 256 núcleos, algo ainda não confirmado pela empresa. Os chips devem usar o processo de fabricação Intel 18A e contar com núcleos Panther Cove do tipo P-Core.

As primeiras informações de plataforma indicam consumo que pode chegar a 650 watts, usando o soquete LGA 9324 e com suporte a múltiplos processadores no mesmo sistema. A previsão é que a Intel apresente oficialmente o Diamond Rapids entre a metade e o segundo semestre de 2026.