A Lei de Moore perdeu ritmo, mas o desenvolvimento de chips continua. Um novo roadmap indica que processos abaixo de 1nm devem surgir por volta de 2034.

Vai demorar até os processos ficarem abaixo de 1nm, mas eles já estão em desenvolvimento: 0,7nm em 2034 e menos de 0,2nm em 2046

A evolução dos processos de fabricação desacelerou com a chegada da era Angstrom. Os nós mais novos ainda trazem ganhos, mas o custo de produção aumentou, já que os equipamentos necessários são mais caros.

Além disso, o uso de chiplets com encapsulamento avançado diminuiu a urgência de migrar para nós menores, pois essa abordagem já entrega escala e melhor custo.

O IMEC, centro independente de pesquisa em nanoeletrônica com sede na Bélgica, divulgou um roadmap que cobre dos anos 2020 até 2040. O material mostra as principais mudanças esperadas na indústria de semicondutores.

A Lei de Moore continua, mas em ritmo mais lento

O primeiro roadmap mostra a evolução da densidade lógica entre 1998 e 2026. De 1998 a 2010, a densidade crescia cerca de 50% ao ano, o que significava reduzir pela metade a área de SRAM nesse período.

De 2010 até 2026, o avanço ficou mais linear, com pouca mudança relevante nos últimos anos. Mesmo assim, o mercado pede mais desempenho, o que depende de maior densidade.

![]()

Tecnologias 2.5D e 3D ajudam nisso, mas também têm limites de energia, temperatura e custo. A TSMC, por exemplo, apresentou o SoW (System-on-Wafer), que amplia o modelo CoWoS para chips voltados a alto poder de processamento.

Chips de IA também exigem integração próxima entre processador e memória, com a DRAM tendo papel importante nesse cenário. Mesmo com o avanço dos chiplets e do encapsulamento, os processos lógicos continuam evoluindo.

- Leia tambem: Elon Musk diz que projeto Terafab foi criado porque a TSMC não consegue atender a demanda de chips

O roadmap do IMEC foca mais em pesquisa e mostra quando novas tecnologias devem ficar prontas. As datas não indicam produção em massa, mas sim o estágio de desenvolvimento.

A era abaixo de 2nm

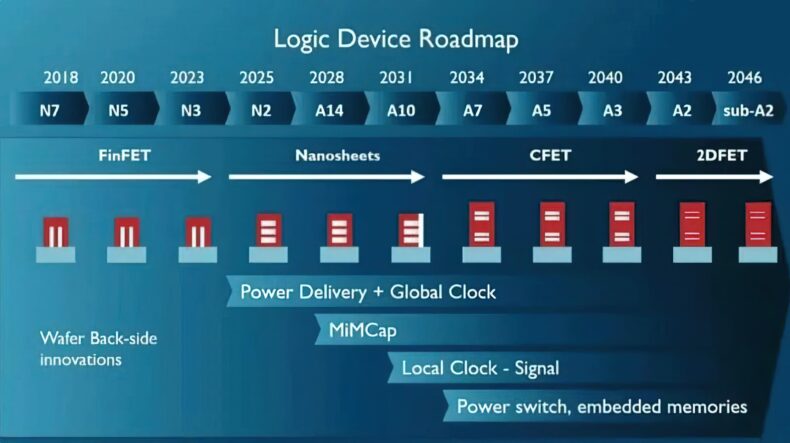

O roadmap começa com os nós baseados em nanosheets, que usam transistores do tipo GAA (Gate-All-Around). Essa tecnologia estreia com o N2 da TSMC, que começa a ser lançado este ano.

A produção em larga escala já está em andamento, e os próximos nós abaixo de 2nm devem ficar prontos até o fim do ano. TSMC e Intel planejam lançar várias versões abaixo de 2nm. No caso da TSMC, estão previstos A16, A14, A13 e A12.

A Intel trabalha com o 14A e suas variações. O último nó com nanosheets deve ser o A10, por volta de 2031, abrindo caminho para a fase abaixo de 1nm.

A era abaixo de 1nm

Nos processos abaixo de 1nm, a expectativa é usar CFETs (transistores complementares), que empilham estruturas de nanosheets na vertical. Isso reduz o tamanho das células e aumenta a densidade de transistores.

O primeiro nó com CFET deve surgir em 2034, com cerca de 0,7nm (A7). Depois disso, o roadmap aponta A5 (0,5nm) em 2036 e A3 (0,3nm) em 2040. Com a evolução dessa tecnologia, a densidade pode crescer até 80%.

Depois vem a era de 2 angstroms, com transistores 2D. Nessa fase, entram novos materiais para formar estruturas 2D, tanto em CFET quanto em nanosheets.

O primeiro uso deve acontecer em 2043 com o nó A2 (0,2nm), seguido por tecnologias abaixo disso até 2046. Como se trata de projeção, prazos podem mudar ao longo do desenvolvimento.

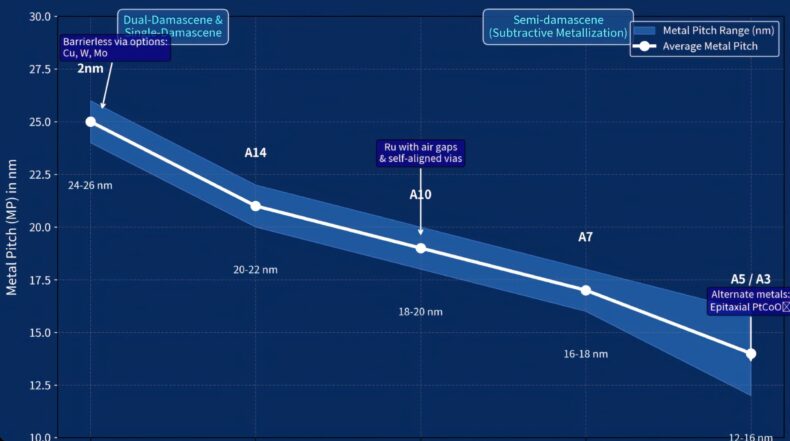

O roadmap também aborda a evolução do BEOL (parte responsável pelas conexões entre transistores). Hoje, o padrão usa cobre com técnicas como Dual-Damascene e Single-Damascene, com espaçamento entre 24 e 26nm.

Esse modelo deve evoluir até 2028, com redução para 20–22nm. Com o avanço dos nós de 1nm e menores, a indústria deve migrar para métodos como Semi-damascene e metalização por subtração.

O rutênio (Ru) deve substituir o cobre, com uso de espaços de ar e conexões mais precisas. Isso reduz a resistência elétrica e melhora a condução.

Nos nós de 0,5nm e menores, entram materiais alternativos como o PtCoO₂ epitaxial (óxido de platina e cobalto) sobre safira. Esses materiais trabalham com espaçamentos ainda menores, entre 16nm e 12nm.

- Leia tambem: Apple pode apresentar chips abaixo de 1nm em alguns anos; TSMC deve iniciar produção de testes em 2029

| Ano | Nó | Metal Pitch (MP) | Tipo de Processo | Principal Inovação |

|---|---|---|---|---|

| 2025 | 2nm | 24–26nm | Dual-Damascene & Single-Damascene | Vias sem barreira (Cu, W, Mo) |

| 2028 | A14 | 20–22nm | Dual-Damascene & Single-Damascene | — |

| 2031 | A10 | 18–20nm | Transição → Semi-damascene | Ru com gaps de ar + vias autoalinhadas |

| 2034 | A7 | 16–18nm | Semi-damascene (Subtrativo) | Ru com gaps de ar + vias autoalinhadas |

| 2037 | A5 / A3 | 12–16nm | Semi-damascene (Subtrativo) | Metais alternativos (ex: PtCoO₂ epitaxial) |

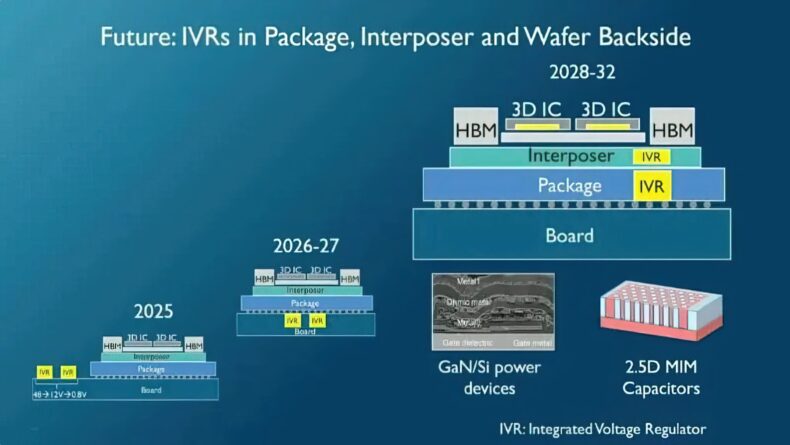

A parte de energia também aparece no roadmap até 2032. A ideia é mover os reguladores de tensão (IVR), que hoje ficam na placa-mãe, para dentro do próprio circuito.

Esses componentes devem reduzir a tensão de 48V para 12V e depois para cerca de 0,8V. Entre 2026 e 2027, os IVRs passam a ficar dentro da placa, logo abaixo do chip principal.

Esse chip abriga o interposer usado em soluções 3D e memórias DRAM. De 2028 a 2032, esses sistemas devem ficar integrados ao próprio pacote, usando tecnologias como capacitores MIM 2.5D e novos dispositivos de energia.

Capacitores MIM já são usados pela Intel em soluções como EMIB, que também integra energia e lógica via conexões internas.

| Ano | Nó | Arquitetura / Transição | Principais Características | Especificações Técnicas (BEOL e Materiais) | Contexto / Observações |

|---|---|---|---|---|---|

| 2018 | N7 (7nm) | FinFET | Primeiro nó FinFET em produção em massa no roadmap | Área de célula SRAM: 0,025–0,023 μm² | Evolução contínua da lógica |

| 2020 | N5 (5nm) | FinFET | Continuação do FinFET com ganho de densidade e desempenho | Melhorias em densidade e desempenho | Foco em IA e HPC |

| 2023 | N3 (3nm) | FinFET | Último nó FinFET; estabilidade na área de SRAM | Área de SRAM estável | Início da escala vertical (3D) |

| 2025 | N2 (2nm) | Nanosheet FETs (GAA) | Transição para transistores Gate-All-Around | Pitch BEOL: 24–26nm (cobre, damascene) | Início da escala vertical |

| 2028 | A14 (1,4nm / 14 Å) | Nanosheet aprimorado (GAA) | Otimização para maior densidade | Pitch BEOL: 20–22nm | Continuação da escala vertical |

| 2031 | A10 (1,0nm / 10 Å) | Nanosheet contínuo | Novos materiais e técnicas para energia e calor | Pitch BEOL: 18–20nm; Ru, gaps de ar, vias autoalinhadas | Controle de consumo de energia |

| 2034 | A7 (0,7nm / 7 Å) | CFET | Empilhamento vertical de transistores p e n | Pitch BEOL: 16–18nm (Ru + gaps de ar) | Primeiro nó CFET |

| 2037 | A5 (0,5nm / 5 Å) | CFET contínuo | Otimizações para HPC e controle térmico | Pitch BEOL: 12–16nm (em desenvolvimento) | Foco em IA e alto desempenho |

| 2040 | A3 (0,3nm / 3 Å) | CFET contínuo | Maior nível de integração | Baseado nas melhorias do A5 | Escala de densidade a longo prazo |

| 2043 | A2 (0,2nm / 2 Å) | FET 2D | Uso de materiais 2D no canal do transistor | Fim da era tradicional do FinFET | Primeira geração 0,2nm |

| 2046 | <0,2nm | FET 2D contínuo | Miniaturização máxima com materiais 2D | Máxima densidade com integração 3D | Visão de longo prazo |

O conjunto desses roadmaps mostra que, mesmo com limites físicos mais próximos, a evolução dos chips continua com uso de empilhamento 3D, novos materiais e mudanças na arquitetura.

Isso deve sustentar ganhos de densidade, desempenho e eficiência por vários anos, com foco em aplicações de IA, computação de alto desempenho e outras áreas.