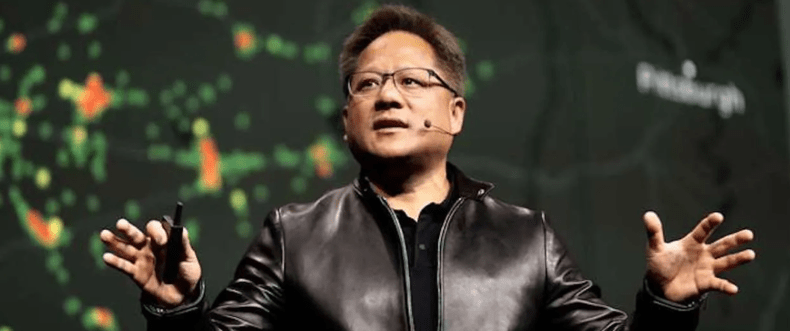

Segundo a imprensa de Taiwan, a TSMC, gigante de fabricação de chips, rejeitou um pedido do CEO da NVIDIA, Jensen Huang, para criar uma linha de produção exclusiva para a embalagem dos produtos da NVIDIA.

Hoje, a embalagem de chips com CoWoS (Chip-em-Wafer-em-Substrato) é considerada um fator tão importante quanto a fabricação dos semicondutores, principalmente com a crescente demanda por chips de IA.

No entanto, essa demanda tem pressionado a capacidade de embalagem da TSMC, levando a empresa a investir pesadamente nesse setor.

Em sua última teleconferência de resultados, a TSMC deixou evidente a importância da embalagem, redefinindo seu mercado para incluir a montagem de chips como uma grande fonte de receita.

Pedido de linha exclusiva para CoWoS gera tensão entre NVIDIA e TSMC

De acordo com um relatório do UDN, durante uma visita à sede da TSMC, Jensen Huang pediu que a empresa montasse uma linha de empacotamento exclusiva para as GPUs da NVIDIA.

Essa visita, que ocorreu no início do ano, incluiu encontros com o fundador da TSMC, Dr. Morris Chang, e o ex-presidente da empresa.

O pedido de Huang gerou discussões acaloradas com os gerentes da TSMC, que levantaram várias questões sobre a viabilidade da solicitação.

As conversas não chegaram a um consenso, e a atmosfera ficou "tensa e embaraçosa", segundo fontes ligada a imprensa de Taiwan.

O papel da embalagem de chips na era da IA

A embalagem de chips tem sido um dos principais desafios na revolução da IA. Analistas já previam essa dificuldade desde o início do entusiasmo com a IA em 2023.

A TSMC tem enfrentado dificuldades para atender à demanda por suas soluções de embalagem, sobretudo devido à alta demanda da NVIDIA e da AMD.

Durante a teleconferência de resultados do segundo trimestre, o CEO da TSMC, Dr. CC Wei, apresentou a nova estratégia da empresa, chamada Foundry 2.0, que inclui fabricação, embalagem, testes e outros serviços além da produção de chips.

Esse novo modelo agrega valor ao mercado de semicondutores, que atingiu US$ 100 bilhões em 2023, com a TSMC detendo 28% desse mercado.

Wei também ressaltou que a capacidade de empacotamento do CoWoS, crucial para os chips da NVIDIA, está no limite e só deve melhorar em 2026. No entanto, o aumento na demanda por embalagem tem impulsionado a margem de lucro da TSMC nesse segmento.

Estrutura da fabricação de semicondutores

A fabricação de semicondutores é dividida em duas partes: front-end e back-end. O front-end envolve a impressão de circuitos em silício, enquanto o back-end engloba todas as operações pós-fabricação, incluindo a embalagem.

A TSMC tem focado nas tecnologias de back-end mais avançadas para apoiar seus clientes na produção de produtos de ponta.

Com a estratégia Foundry 2.0, a TSMC espera aumentar sua participação no mercado e expandir suas capacidades de embalagem, alinhando-se às necessidades de empresas líderes como a NVIDIA.