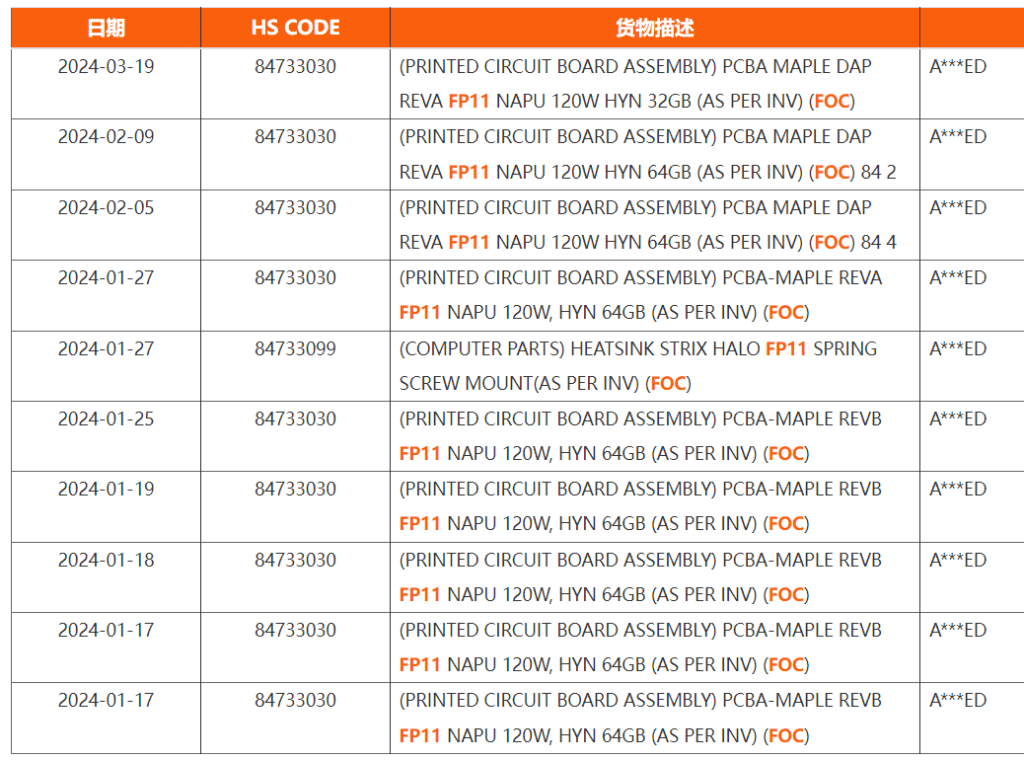

Os APUs Ryzen "Strix Halo" da AMD foram vistos novamente em um manifesto de envio com TDP de até 120 W. Esses APUs serão as ofertas de chiplet da empresa, utilizando até 3 dies, 2 CCDs e 1 GCD.

Os chips terão até 16 núcleos Zen 5 com 32 threads. Esses chips manterão a mesma estrutura de cache L1 e L2, ou seja, um máximo de 16 MB de cache L2, enquanto o cache L3 será aumentado para 32 MB por CCD.

Portanto, podemos ver até 64 MB de cache L3 nos chips superiores (dois CCD). Para o lado do iGPU, os APUs Strix Halo manterão a arquitetura gráfica RDNA 3+, mas virão equipados com 20 WGPs ou 40 unidades de computação.

Além disso, para suportar tais iGPUs high-end em um design de chiplet, também haverá um cache MALL adicional de 32 MB a bordo do IOD que eliminará os gargalos de largura de banda para este iGPU.

Outras especificações incluem suporte para até memória LPDDR5x-8000 (256 bits) e uma NPU "XDNA 2" AI capaz de entregar mais de 70 TOPs.

Os APUs Strix Halo serão centrados nas últimas plataformas FP11. Esses APUs terão TDPs de 70W (cTDP 55W) e suportarão classificações de pico de até 130 W.

Para exibição, tanto os APUs AMD Strix quanto Strix Halo virão com suporte para eDP (DP2.1 HBR3) e DP externo (DP2.1 UHBR10), USBC Alt-DP (DP2.1 UHBR10) e USB4 Alt-DP (DP2.1 UHBR10) como parte de seus motores de mídia. Strix Halo apresentará suporte para até DP2.1 UHBR20.